# Addressing Failures in Exascale Computing

Marc Snir Robert W. Wisniewski Jacob A. Abraham Sarita V Adve Franck Cappello Saurabh Bagchi Pavan Balaji Jim Belak Pradip Bose Bill Carlson Andrew A. Chien Paul Coteus Nathan A. Debardeleben Pedro Diniz Christian Engelmann Mattan Erez Saverio Fazzari Al Geist Rinku Gupta Fred Johnson Sriram Krishnamoorthy Sven Leyffer Jon Stearley Dean Liberty Subhasish Mitra **Todd Munson** Rob Schreiber Eric Van Hensbergen

## **Executive Summary**

The current approach to resilience for large high-performance computing (HPC) machines is based on global application checkpoint/restart. The state of each application is checkpointed periodically; if the application fails, then it is restarted from the last checkpoint. Preserving this approach is highly desirable because it requires no change in application software.

The success of this method depends crucially on the following assumptions:

- 1. The time to checkpoint is  $\ll$  mean time before failure (MTBF).

- 2. The time to restart (which includes the time to restore the system to a consistent state) is  $\ll$  MTBF;

- 3. The checkpoint is correct—errors that could corrupt the checkpointed state are detected before the checkpoint is committed.

- 4. Committed output data is correct (output is committed when it is read).

It was not clear that these assumptions are currently satisfied. In particular, can one ignore silent data corruptions (SDCs)? It is clear that satisfying these assumptions will be harder in the future for the following reasons:

- MTBF is decreasing faster than disk checkpoint time.

- MTBF is decreasing faster than recovery time—especially recovery from global system failures.

- Silent data corruptions may become too frequent, and errors will not be detected in time.

- The output of the application may be used in real time.

Each of these obstacles can be overcome in a different way: (1) we can checkpoint in RAM, rather than disk; (2) we can build global operating systems that fail less frequently or recover faster; (3) we can design hardware with lower SDC rates or, alternatively, use software to detect SDCs or tolerate them; and (4) we can use replication for the relatively rare real-time supercomputing applications.

The different approaches are associated with different costs, risks, and uncertainties; we do not have enough information to choose one approach now. Therefore, we considered the following three design points: (1) business as usual, (2) system-level resilience, and (3) application-level resilience.

**Design point 1: Business as Usual** This approach continues to use global checkpoint/restart. Hybrid checkpoint methods (using DRAM or NVRAM, as well as disk) can provide fast checkpoint and application restart time and can accommodate failure rates that are an order of magnitude higher than today's failure rates. The additional power consumption is low, but the acquisition cost of platforms will rise because of the need for additional memory.

Two key technologies are needed for this approach to be feasible. (1) low SDC frequency (same as now) and low frequency of system failures or an order of magnitude improvement in system recovery time.

Maintaining the current rate of hardware SDC seems possible, at the expense of <20% of additional silicon and energy; and vendor research can further lower the overhead. However, supercomputing needs both low power and low SDC rate. It is not clear that there is a large market for this combination; hence it is not clear that this combination will appear in lower-cost volume products.

Silent hardware errors can be masked in software—the simple approach is to duplicate computations and compare results. Since most compute time and compute energy are spent moving data, a good hardware/software combination should enable the duplication of computation at a cost that is much less than

100%, as data movement need not be replicated. Such combined solutions might be more if they provide the user with a choice of higher performance or higher reliability.

Reducing system failures or system recovery time seems feasible but requires new research. This includes development of fault-tolerance mechanisms that avoid or mitigate failures due to hardware or software. A significant body of knowledge in this area exists but has not been applied to HPC; research should focus on the new problems that are likely to arise with this new application.

**Design point 2: System-Level Resilience** This approach assumes that vendors will not provide sufficiently low SDC rates at an acceptable acquisition and operation cost but that a combination of hardware and software technologies can hide the increased failure rates from the application.

Various techniques are available for detecting SDCs in software, and applications can tolerate some SDCs. This design point is not fundamentally different from the first one. It does, however, give more leeway to vendors on selecting where they apply hardware and where they apply software solutions. It also calls on the wider system software community to develop resilience capability for runtimes and libraries.

**Design point 3: Application-Level Resilience** This approach assumes that application codes will need to be modified in order to handle the increased failure rate, since neither hardware nor firmware will be efficient enough in avoiding SDCs. The critical need is for codes that can tolerate SDCs or detect SDCs.

Significant research does exist in this area, but the research is focused on specific algorithms and methods. It is not clear that current approaches can cover a large fraction of DOE's workloads.

**Recommendations:** Any future solution to the resilience problem must be rooted in a clear understanding of the current situation: What is the cause of failures, and what is the frequency of SDC? This information is not readily available. Thus, we make the following recommendations.

**Recommendation 1:** Perform experiments to estimate SDC rates on current platforms. Collect, in a consistent manner, information on detected failures on current large DOE systems and make it available to researchers in a suitable form.

The main downside of the first design point is the potential cost of platforms using this approach; the second and, especially, the third design points have risks in terms of problems with no known solutions. The three design points motivate fairly different investment streams.

**Recommendation 2:** Work with industry to refine estimates on cost (design complexity, transistors, power) of keeping SDC rates low and to understand the market opportunities for low-power, high-resilience technology. Aim for an early decision on levels of error detection and correction that will be provided by hardware. Invest in research on combined hardware/software error detection that is transparent to the user.

Some technologies are required no matter what design point is picked; some are beneficial no matter what design point is picked. In the first category is the need for more robust system software infrastructure and for faster system recovery, as well as good support for hybrid checkpoints. In the second category is fault prediction that increases the effective MTBF and, therefore, reduces the cost of fault tolerance.

**Recommendation 3:** Invest first in R&D for technologies that are required or beneficial no matter what design point is picked.

Solutions must apply to all or to the large majority of DOE's workloads. A solution that is specific to a subset of these workloads can, at best, accelerate the execution of these workloads but will not avoid the need for developing a general solution.

**Recommendation 4:** Focus research on application-level error handling to solutions that can apply to all or to the large majority DOE workloads. Point solutions that address specific codes should be a second priority.

## Contents

| 1 | Intro | oduction                                                                                  | 6 |

|---|-------|-------------------------------------------------------------------------------------------|---|

|   | 1.1   | The Problem of Resilience at Exascale                                                     | 6 |

|   | 1.2   | Applicable Technologies                                                                   | 7 |

|   | 1.3   | The Solution Domain                                                                       | 7 |

|   | 1.4   | Previous Reports                                                                          | 8 |

| 2 | Toyo  | onomy of Terms                                                                            | 9 |

| _ | 2.1   |                                                                                           | 9 |

|   | 2.2   | Life Cycle and Operational Status                                                         |   |

|   | 2.3   | Failure Characteristics                                                                   |   |

|   | 2.3   | Fault Characteristics                                                                     |   |

|   | 2.5   | Error Characteristics                                                                     |   |

|   | 2.6   | Means of Dealing with Faults                                                              |   |

|   | 2.7   | Fault Tolerance Techniques                                                                |   |

|   | 2.7   | *                                                                                         |   |

|   | 2.9   | Metrics         1           Workload         1                                            |   |

|   |       |                                                                                           |   |

|   |       | Availability                                                                              |   |

|   | 2.11  | Subsystem                                                                                 |   |

|   |       | Statistical Models                                                                        |   |

|   | 2.13  | Resilience, Fault Tolerance, and Dependability                                            | ) |

| 3 | Sour  | rces and Rates of Hardware Faults and Errors 1                                            | 5 |

|   | 3.1   | Generic Machine Model and Associated Errors and Failures                                  | 5 |

|   | 3.2   | Classification of Errors and Failures                                                     | 6 |

|   | 3.3   | Quantification of Component Errors and Failures                                           | 7 |

|   | 3.4   | Hardware Fault, Error, and Failure Models and Projections                                 | 8 |

|   |       | 3.4.1 Compute Node Soft Errors                                                            | 8 |

|   |       | 3.4.2 Compute Node Hard Errors and Failures                                               | 3 |

|   |       | 3.4.3 Network                                                                             | 4 |

|   |       | 3.4.4 I/O                                                                                 | 5 |

|   | 3.5   | Commercial Trends                                                                         | 5 |

|   | 3.6   | Shielding                                                                                 | 5 |

|   | a     |                                                                                           | , |

| 4 |       | ces and Rates of Software Faults and Errors  Classes of Software Faults                   |   |

|   | 4.1   | Classes of Software Faults                                                                |   |

|   |       |                                                                                           |   |

|   |       | 4.1.2 Class 2: Hardware propagating up to software and software not handling it correctly |   |

|   | 4.0   | 4.1.3 Class 3: Software creating a problem for the hardware                               |   |

|   | 4.2   | Severity of Software Faults                                                               |   |

|   | 4.3   | Evolution of Failure Types and Rates at the Exascale                                      | 8 |

| 5 | Erro  | r Prevention, Detection, and Recovery 2                                                   | 8 |

|   | 5.1   | Prevention                                                                                | 9 |

|   | 5.2   | Prediction                                                                                | 9 |

|   | 5.3   | Tolerance                                                                                 | 0 |

|   | 5.4   | Detection                                                                                 | 1 |

| В | Deri       | ivation of Optimal Checkpoint Interval                                                                                         | 1    |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------|------|

| A | Taxe       | onomy Summary Sheet                                                                                                            | 52   |

|   | 8.3        | Integration                                                                                                                    | . 51 |

|   |            | 8.2.3 Scenario-Specific Technologies                                                                                           | . 51 |

|   |            | 8.2.2 Generally Useful Technologies                                                                                            |      |

|   |            | 8.2.1 Necessary Technologies                                                                                                   |      |

|   | 8.2        | Research Areas                                                                                                                 |      |

|   |            | 8.1.3 Refinement of Estimates on Future Hardware Technologies                                                                  |      |

|   |            | 8.1.2 Study of Frequency of Silent Errors                                                                                      |      |

|   | 0.1        | 8.1.1 Characterization of Sources of Failures on Current Systems                                                               |      |

| ø | 8.1        | Information Gathering                                                                                                          |      |

| 8 | Suga       | gested Actions                                                                                                                 | 49   |

|   | 7.3        | Application Scenarios                                                                                                          | . 48 |

|   | 7.2        | System Software Scenario                                                                                                       |      |

|   | 7.1        | Base Scenario                                                                                                                  |      |

| 7 | Poss       | sible Scenarios                                                                                                                | 46   |

|   | 0.0        | Zenem ep or Enough                                                                                                             |      |

|   | 6.6        | Bottom-Up View of Errors                                                                                                       |      |

|   | 6.5        | Top-Down View of Errors                                                                                                        |      |

|   | 6.4        | Fault/Error Propagation and Security Implications                                                                              |      |

|   | 6.3        | Responding to and Handling of Faults/Errors                                                                                    |      |

|   |            | <ul><li>6.2.1 Error Management: Algorithm Hints and Watchpoints</li><li>6.2.2 Error Management: Communication Errors</li></ul> |      |

|   | 6.2        | Reporting of Software-Detected Errors                                                                                          |      |

|   | 6.1        | Fault and Error Management                                                                                                     |      |

| 6 | •          | tem View of Resilience                                                                                                         | 41   |

|   | <b>C</b> . | 77 CT 11                                                                                                                       |      |

|   |            | 5.6.7 Rejuvenation                                                                                                             | . 40 |

|   |            | 5.6.6 Accommodation of Errors Based on Naturally Redundant Information                                                         |      |

|   |            | 5.6.5 Fault-Tolerant MPI                                                                                                       |      |

|   |            | 5.6.4 Application and Algorithmic Recovery                                                                                     |      |

|   |            | 5.6.3 Fault-Tolerant Data Structures                                                                                           |      |

|   |            | 5.6.2 Localized Restart                                                                                                        |      |

|   | 5.0        | 5.6.1 Restart                                                                                                                  |      |

|   | 5.6        | Recovery                                                                                                                       |      |

|   |            | 5.5.2 System Software                                                                                                          |      |

|   | 3.3        | Containment                                                                                                                    |      |

|   | 5.5        | 5.4.3 Behavioral-Based Detection                                                                                               |      |

|   |            | 5.4.2 Application-Level Detection of Hardware Errors                                                                           |      |

|   |            | 5.4.1 Software-Driven Detection of Hardware Errors                                                                             |      |

|   |            | TAI OO DI DII DI II D                                                                                                          | 0.1  |

#### 1 Introduction

"The problems are solved, not by giving new information, but by arranging what we have known since long." – Ludwig Wittgenstein, *Philosophical Investigations*

This white paper is the result of the workshop on "Addressing Failures in Exascale Computing" held in Park City, Utah, August 4–11, 2012. The workshop was sponsored by the Institute for Computing in Science (ICiS). More information about ICiS activities can be found at http://www.icis.anl.gov/about. The charter of this workshop was to establish a common taxonomy about resilience across all the levels in a computing system; to use that common language in order to discuss existing knowledge on resilience across the various hardware and software layers of an exascale system; and then to build on those results, examining potential solutions from both a hardware and software perspective and focusing on a combined approach.

The workshop brought together participants with expertise in applications, system software, and hardware; they came from industry, government, and academia; and their interests ranged from theory to implementation. The combination allowed broad and comprehensive discussions and led to this document, which summarizes and builds on those discussions.

The document is organized as follows. In the rest of the introduction, we define resilience and describe the problem of resilience in the exascale era. In Section 2, we present a consistent framework and terms used in the rest of the document. Sections 3 and 4 describe the sources and rates for hardware and software errors. Section 5 examines classes of software capability in preventing, detecting, and recovering from errors. Section 6 takes a systemwide view and describes possible ways of achieving resilience. Section 7 presents possible scenarios and how to handle failures. Section 8 provides suggested actions.

#### 1.1 The Problem of Resilience at Exascale

DOE and other agencies are engaged in an effort to enable exascale supercomputing performance early in the next decade. Extreme-scale computing is essential for progress in many scientific and engineering areas and for national security. However, progress from current top high-performance computing (HPC) systems (at tens of petaflops peak performance and roughly 1 PF sustained performance) to systems 1,000 times more powerful will encounter obstacles. One of the main roadblocks to exascale is the likelihood of much higher error rates, resulting in systems that fail frequently and make little progress in computations or in systems that may return erroneous results. Although such systems might achieve high nominal performance, they would be useless.

Higher error rates will be due to a confluence of many factors:

- Hardware failures are expected to be more frequent (discussed in more detail in Section 3). Errors undetected by hardware may be frequent enough to affect many computations.

- As hardware becomes more complex (heterogeneous cores, deep memory hierarchies, complex topologies, etc.), software will become more complex and hence more error-prone. Failure and energy management also add complexity. In addition, the larger scale will add complexities as more services need to be decentralized, and complex failure modes that are rare and ignored today will become more prevalent.

- Application codes are becoming more complex. Multiphysics and multiscale codes couple an increasingly large number of distinct modules. Data assimilation, simulation, and analysis are coupled into increasingly complex workflows. Furthermore, the need to reduce communication, tolerate asynchrony, and tolerate failures results in more complex algorithms. The more complex libraries and application codes are more error-prone. Software error rates are discussed in Section 4 in more detail.

#### 1.2 Applicable Technologies

The solution to the problem of resilience at exascale will require a synergistic use of multiple hardware and software technologies.

Avoidance: for reducing the occurrence of errors

**Detection:** for detecting errors as soon as possible after their occurrence

**Containment:** for limiting the impact of errors

**Recovery:** for overcoming detected errors

Diagnosis: for identifying the root cause of a detected error

**Repair:** for repairing or replacing failed components

We discuss potential hardware approaches in Section 3 and potential software solutions to resilience in Section 5.

#### 1.3 The Solution Domain

The current approach to resilience assumes that silent errors are rare and can be ignored. Applications checkpoint periodically; when an error is detected, system components are either restored to a consistent state or restarted; applications are restarted from the latest checkpoint. We divide the set of possible solutions for resilience at exascale into three categories.

**Base Option:** Use the same approach as today. This would require the least effort in porting current applications but may have a cost in terms of added hardware and added power consumption. We discuss in Section 7.1 what improvements are needed in hardware and system software in order to carry this approach into the exascale range, and we consider what costs will be incurred.

**System Option:** Use a combination of hardware and system software to handle resiliency in a manner that is transparent to the application developer. This approach will require no change in application codes and is therefore equivalent to the base option from the viewpoint of application developers. The relative cost of hardware changes vs. system software changes will dictate preferences between the base option and the system option. We discuss this option in Section 7.2.

**Application Option:** Require application developers to handle resilience as part of their application code. The approach is more invasive from the viewpoint of application developers but may reduce the cost of exascale platforms and their energy consumption. We further subdivide this option into two suboptions.

**Application-Level Error Detection** Application code is responsible for error detection; recovery is done, as today, by restarting from a checkpoint. That is, the only added burden on application developers is to provide a checkpoint validation routine. We discuss this option in Section 7.3.

**Application-Level Error Correction** Application code is also written so as to avoid the need for global checkpoint and global restart, thus possibly reducing the overheads entailed by this approach. We discuss this option in Section 5.6.4.

We find that some technologies are essential no matter which approach is chosen. For example, it is essential to reduce the frequency of system crashes and to reduce the time to recover from system crashes. Other technologies are "no brainers" in that they improve the resilience of systems with little added cost. This is true, for example, of failure prediction and avoidance, as discussed in Section 5.1.

The three options are not mutually exclusive. The system option will still require adequate hardware support, and the application option will require adequate hardware and system software support. Design choices will need to consider the maturity of various technologies and the relative cost of the different choices of higher platform acquisition cost, higher power consumption, or higher cost for application code development and porting. The balance may change over time and may well not be the same for today's 10 PF machines as for a 100 PF system or an exascale system. To be able to make the tradeoffs requires understanding the costs based on the expected and possible capabilities at each layer. Thus, we discuss in Section 8 the commonality between these options, pointing out technologies that are clearly needed no matter what path is taken, and the research, observations, and experiments that can help us choose the appropriate path.

#### 1.4 Previous Reports

Our work leverages several recent reports on resilience.

A DARPA white paper on system resilience at extreme scale was issued in 2008 [40]. It points out that current high-end system wastes 20% of its computing capacity on failure and recovery. The white paper outlines possible evolutionary and revolutionary research with the goal of bringing this number down to 2%.

A DOE/DOD report issued in 2009 [32] identifies resilience as a major emerging issue for high-end computing (HEC) that requires new approaches. It calls for a national effort and proposes research in five thrust areas: theoretical foundations, enabling infrastructure, fault prediction and detection, monitoring and control, and end-to-end data integrity. This report considers resilience to be "concerned with reliability of information in lieu of, or even at the expense of, reliability of the system."

A DOE/DOD report issued in 2012 [37] identifies six high priorities: fault characterization, detection, fault-tolerant algorithms, fault-tolerant programming models, fault-tolerant system services, and tools.

The Computing Community Consortium (CCC) organized in 2011 a Cross-Layer Reliability Visioning Study [6]. This study, while not focused on high-performance computing, makes many relevant points. It suggests a research and education program with eight components: repairable hardware architectures; cross-layer information sharing; multilayer error filtering; multilayer tradeoffs for error handling; differential reliability; techniques, theories, and platforms that are scalable and adaptive to a wide range of error rates and error types; graceful degradation; and embedding of reliability and immunologics engineering into electrical engineering, computer engineering, and computer science curricula.

A recent DOE workshop [56] focused on resilience from the perspective of DOE, with the following goals: (1) describe the required HPC resilience for critical DOE mission needs; (2) detail what HPC resilience research is already being done at the DOE national laboratories and is expected to be done by industry or other groups; (3) determine what fault management research is a priority for DOEs Office of Science and NNSA over the next five years; and (4) develop a roadmap for getting the necessary research accomplished We included in this list only recent reports. We note, however,

that research on fault-tolerant computing is as old as computers are. Frequent failures were a major problem in the earliest computers: ENIAC had an MTTF of two days [148]. Major advances in this area occurred in the 1950s and 1960, for example, in the context of digital telephone switches [36] and mainframes [143]. Bibliographical research must be an important component of a research program in resilience.

### 2 Taxonomy of Terms

Editor: Jon Stearley Contributors: Rinku Gupta

"Clear language engenders clear thought." - Richard Mitchell, The Underground Grammarian

The absence of agreed upon definitions and metrics for supercomputer reliability, availability, and serviceability has, in the past, obscured meaningful discussion of the issues involved and has hindered their solution [145]. In order to avoid similar confusion, several of the participants were asked to address terminology a few weeks ahead of the workshop. In subsequent email discussions, it was proposed that the taxonomy of Aviženis [9] be considered as a widely used standard to build upon (having roughly 2,000 citations). A summary sheet was prepared and then discussed on the first day of the workshop; it is appended to this report. Several omissions and corrections were identified during the discussion, but there was wide consensus that the taxonomy was sufficiently clear and complete to be used as a basis of our discussion of addressing failures at exascale. Additional revisions were made during the week based on subsequent discussions, and the resulting definitions appear below.

#### 2.1 Dependability

The definitions in this section are based almost entirely on [9].

System: an entity that interacts with other entities

**Component/subsystem:** a system that is part of a larger system

**Atomic component:** the point at which system/component recursion stops, by desire or discernability

**Functional specification:** description of system functionality and performance, defining the threshold between a *correct* and an *incorrect* service (acceptable vs unacceptable)

**Service:** a system's externally perceived behavior

**Quality of service (QoS):** guarantees provided by the system on the performance and reliability of the service it provides

**Behavior:** what a system does to implement its function, described by a series of states

**Total state:** a system's computation, communication, stored information, interconnection, and physical condition

**Dependability:** the ability to avoid service failures that are more frequent and more severe than is acceptable

**Dependence:** the extent to which a system's dependability is affected by another's

Trust: accepted dependence

The terms fault, error, and failure are sometimes used synonymously, but we believe that more distinctive use, as defined in [9], is beneficial:

**Fault:** the cause of an error (e.g., a bug, stuck bit, alpha particle)

**Error:** the part of total state that *may* lead to a failure (e.g., a bad value)

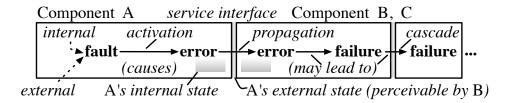

Figure 1: Error propagation and cascading failures

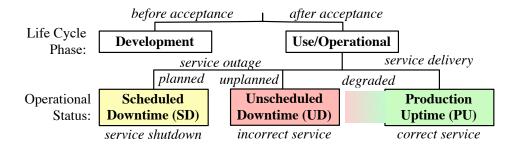

Figure 2: System's operational status

Failure: a transition to incorrect service (an event, e.g., the start of an unplanned service outage)

#### Degraded mode/partial failure the failure of a subset of services

Faults can be *active* or *inactive*, meaning actually causing errors or not. A fault is generally local to a single component, as distinct from errors that may propagate from component to component. Similarly, the failure of one component may lead to the failure of another (e.g., "cascading" failures), as shown in Figure 1.

For example, consider a cracked wire inside a cable. The crack is the fault, and it does not move from cable to cable. Because of the crack, a certain bit may be incorrectly flipped during transmission, resulting in an error (an incorrect bit value). The cable failed to provide correct service. The error may continue to propagate from device to device, perhaps leading to incorrect results (a failure). Or that flipped bit may have no effect on final results (no failure).

#### 2.2 Life Cycle and Operational Status

After acceptance, a system is, at any time, in one of the operational states shown in Figure 2.

#### 2.3 Failure Characteristics

**Domain:** What has failed. The failure can be involve the wrong *content* (incorrect state) or wrong *timing*—service not provided in a timely manner.

**Persistence:** A failed system may *halt* (fail-stop) or may exhibit an *erratic* behavior.

**Detectability:** A failure can be *signaled* once it is detected and a warning is generated; otherwise, it is *unsignaled*. The detection and signaling mechanism can fail, resulting in *false positives* (a false alarm) or a *false negative* (a failure that did not generate an alarm). The *precision* of a detection mechanism is the fraction of signaled failures that were actual failures, and *recall* is the fraction of failures that were detected and signaled: precision  $= 1 - \text{false\_positives/signalled}$ ; and recall  $= 1 - \text{false\_negatives/failures}$ .

**Consistency:** A failure is *consistent* if it is perceived identically by all users; it is *inconsistent* (or Byzantine) if it is perceived differently by different users. Fail-stop errors are normally consistent, whereas erratic failures can lead to Byzantine behavior.

#### 2.4 Fault Characteristics

Active: Fault causes an error.

**Dormant:** Fault does not cause an error. The dormant fault is *activated* when it causes an error.

**Permanent** Presence is continuous in time.

**Transient** Presence is temporary.

**Intermittent** Fault is transient and reappears.

Hard/solid: Activation is systematically reproducible.

**Soft/elusive:** Activation is not systematically reproducible.

The distinction between hard and soft faults is not a strict one: Faults may be due to a complex combination of internal state and external conditions that occur rarely and are difficult to reproduce; they appear as soft faults; a root cause analysis may identify the precise circumstances of the fault, enabling systematic reproduction.

#### 2.5 Error Characteristics

**Detected:** indicated by error message or signal

Latent/silent: not detected

**Masked:** not causing a failure

**Soft:** due to a transient fault

#### 2.6 Means of Dealing with Faults

Forecasting: to estimate the present number, future incidence, and likely consequences of faults

**Prevention:** to prevent fault occurrence

**Removal:** to reduce fault number and severity

**Tolerance:** to avoid service failures in the presence of faults

#### 2.7 Fault Tolerance Techniques

Error detection: identify the presence of an error

Concurrent: occurs during service delivery

**Preemptive:** occurs during planned service outage

**Recovery:** prevent faults from causing failures

**Error handling:** eliminate errors

**Rollback:** revert to previous correct state (e.g., checkpoint, retry)

**Rollforward:** move forward to a new correct state **Compensation:** correct the error (e.g., via redundancy)

**Fault handling:** prevents faults from reactivating **Diagnosis:** identifies fault location and type

**Isolation:** excludes from interaction with other components **Reconfiguration:** replaces component or moves work elsewhere **Reinitialization:** performs a pristine reset of state (e.g., reboot)

Error detection identifies the presence of an error but does not necessarily identify which part of the system state is incorrect, and what fault caused this error. By definition, every fault causes an error. Almost always, the fault is detected by detecting the error this fault caused. Therefore, "fault detection" and "error detection" are often used synonymously.

"Full diagnosis" identifies the root cause of a failure—the original fault or faults that caused this failure; on the other hand, "partial diagnosis" traces back the error to previous events in the causality chain but does not necessarily identify the original fault. Thus, failure of a software system may be traced back to a hardware error, such as a bit flip, without identifying the fault that caused this bit flip.

#### 2.8 Metrics

If you can not measure it, you can not improve it. - Kelvin

We cannot optimize resilience without measuring it. We discuss here two metrics: workload and availability.

#### 2.9 Workload

A key metric is the ratio of the ideal time to solution on an ideal, fault-free system  $(T_{solve})$  to the actual runtime in a real system  $(T_{wallclock})$ :

Workload Efficiency =  $T_{solve}/T_{wallclock}$ .

In the general case, where the system is running a mix of jobs, we can define workload efficiency as the ratio between the ideal time to solution for this job mix on a fault-free system and the actual running time. The difference between  $T_{wallclock}$  and  $T_{solve}$  is the *overhead* associated with dealing with faults, errors, and failures, including scheduled downtime, unscheduled downtime, and the cost of detection, diagnosis, repair, compensation, and time lost because of degraded performance.

Typically, workload efficiency is measured with respect to "system faults" and includes all faults underlying applications that impact solution correctness or solution time: software bugs, hardware bugs, hardware faults, and so forth. It does not include faults such as application bugs or user errors. However, the workload efficiency does depend on the application code. For example, it depends on how frequently the user checkpoints and how efficient the checkpoint and restart code are. If failure handling will require increased user involvement in the future, then workload efficiency will increasingly depend on the user code, but the overhead due to user code that handles failures will be increasingly hard to measure.

The workload efficiency metric is an "instantaneous metric." The workload efficiency of a system will vary over time: failure rates are higher on a new system or on a system close to the end of its lifetime. Better system design and better testing procedures may reduce the time needed to stabilize a system and raise the workload efficiency faster. Therefore, it is also useful to define a total workload efficiency metric

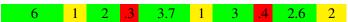

up-time – time when the system functions as specified \_\_\_\_\_ scheduled down-time unscheduled down-time

Figure 3: System history

that integrates workload efficiency over the lifetime of a system. The definition of such an integrated metric has to take into account that computers depreciate rapidly: a flop now is twice as valuable as a flop in two to three years; hence overhead now is twice as expensive as overhead in two to three years. Given a depreciation rate, it is easy to compute a depreciated total workload efficiency.

The definition of workload efficiency considers time as the critical system resource. If energy is the critical resource, then workload efficiency can be defined as the ratio of the energy needed to solve a problem in an ideal, fault-free system, to the energy needed in reality. Considering the impact of wasted energy is important: Some of the techniques for recovery discussed in this report could have little effect on total wall-clock time but could significantly reduce power consumption.

In practice, both time and energy are important resources, as are the acquisition cost of the system and the additional program development effort needed to handle failures. The contribution of resilience technology to the value of supercomputers can be measured by a "total factor productivity" (TFP) metric, as the ratio between the cost of inputs (acquisition price, salaries, electricity bills) and the value of outputs (scientific results) [141]). Unfortunately, it is hard to properly estimate the cost of various inputs (e.g., programming time), even harder to separate the contribution of resilience technology from the contribution of other technologies, and practically impossible to put a price on the output of supercomputers.

#### 2.10 Availability

Availability metrics are similar in spirit but more operational in nature. For example, a system may be defined to be "down" when more than 5% of the compute nodes are down or the file system is down; downtime may be considered "unscheduled" if notification occurs less than 12 hours in advnace[105].

Consider the time series in Figure 3 of system states, where numbers indicate duration in days. We tabulate the data into sets and obtain the following statistics:

| $\int$ Set $X$                                | $\sum X$                     | X                |

|-----------------------------------------------|------------------------------|------------------|

| <i>Uptime periods</i> ={6, 2, 3.7, 3, 2.6}    | Uptime = 17.3                | NumUptimes = 5   |

| Scheduled downtime periods={1, 1, 2}          | $Scheduled\_Downtime = 4$    | NumSchedDown = 3 |

| <i>Unscheduled downtime periods</i> ={.3, .4} | $Unscheduled\_Downtime = .7$ | NumInterrupts=2  |

|                                               | $Total\_Time = 22$           |                  |

The following metric is recommended as a *control* (specified) metric [11]:

• *Scheduled Availability =Total\_Time - Scheduled\_Downtime/Total\_Time.*

In our example, Scheduled Availability = (22 - 4)/22 = 81.8%.

The following metric is recommended as an observed metric:

• Actual Availability = Uptime/Total\_Time.

In our example, *Total Availability*= 17.3/22 = 78.6%

We are using *interrupt* as synonymous with detected failure, so *mean time between interrupts* (MTBI) is equal to *mean time between failures* (MTBF). In our example, MTBI = TotalTime/NumInterrupts = 22/2 = 11 days.

Similarly, if MTTI is the mean time to interrupt, then MTTI = Uptime/NumInterrupts = 17.3/2 = 8.65 days.

The mean time to repair (MTTR) is the average length of a unscheduled downtime period. In our example,  $MTTR = Unscheduled\_Downtime/NumInterrupts = .7/2 = .35$  days.

The *mean uptime* is the average length of an uptime period. In our example, MeanUptime = Uptime / NumUptimes = 17.3/5 = 3.46 days.

#### 2.11 Subsystem

When discussing faults, errors, and failures, one must carefully identify what "system" is being referred to. In the previous example, the cable can be considered a system (of wires, solder connections, pins, etc.), the transmission network a whole can be considered a "system" (of cables, switches, network cards), and the entire collection can be considered a "system" (compute nodes, I/O nodes, network, disks, etc.).

The taxonomy [9] was developed to address both dependability and security, so the definitions are extremely broad. For example, "system" can refer not only to computing equipment but also to a hacker or group of collaborating hackers. We found it important to identify what is meant by "system" and to identify when that definition changes during the discussion, such as "full system" versus "I/O system." Some uses of "system" include applications, users, and administrators; but the majority of participants referred to "full system" as the collection of components *underlying* the application (not including the application or elements above it, such as users).

Unique acronyms can increase clarity. For example, Sandia and Los Alamos National Laboratories prepend an "S" (e.g., SMTTI) to metrics that apply to the full system and 'other prefixes to identify subsystems [2, 145]. JMTTI, the *job mean time to interrupt*, is defined as  $JMTTI = (Uptime \times NumJobs)/Num JobInterrupts$ , where NumJobs is the total number of jobs run and NumJobInterrupts is the total number of jobs terminated as a result of any failure. NMTTI, node mean time to interrupt, is defined as  $NMTTI = Uptime \times NumNodes/NumNodeFailures$ , where NumNodes is the total number of nodes and NumNodeFailures is the total number of node failures.

#### 2.12 Statistical Models

Analyses of failures and recovery algorithms assume that failures occur according to a probabilistic process that has a closed-form description. A typical assumption is that failures are independent, that is, failure intervals are independent, identically distributed random variables. This assumption is clearly false over long periods, since failures are more frequent on a new system or on a system close to the end of its expected lifetime (this leads to a so-called bathtub distribution of failures). It is not clear to what extent the assumption is valid over short time periods, since many phenomena may cause correlated failures. In particular, even if faults are independent, some faults may cause cascading failures of many components. For example, a power or cooling fault can cause the failure of a large number of nodes.

It is often assumed that between-failure intervals have an *exponential distribution*, with a cumulative distribution function (CDF)  $F(t) = 1 - e^{-t/M}$ , where M is the MTBI. Such a distribution is implied by the assumption that failures occur according to a Poisson process: The probability that a failure occur during a time interval depends only on the length of this interval. A *Weibull distribution*, with a CDF of  $F(t) = 1 - e^{-(t/M)^k}$ , can be used to model a decreasing failure rate (k < 1), constant failure rate (k > 1), or increasing failure rate (k > 1),

An empirical study of HPC failure data from Los Alamos National Laboratory showed a poor fit to an exponential distribution, whereas gamma or Weibull distributions with decreasing failure rates (.7-.8) fit well [135]. Surprisingly this study showed that the Weibull distribution fit better in the outer years of the observed system, while no distribution fit well in the first years. These results could interpreted as meaning

that failures in HPC systems are chaotic during the long period it takes for the system to stabilize and that the system keeps improving its reliability through its lifetime. Such an interpretation is consistent with the observation that most failures are due to software.

See http://cfdr.usenix.org for this and other data.

#### 2.13 Resilience, Fault Tolerance, and Dependability

Unitl now, we have been using the key term "resilience" without clearly defining it. Several reports [38, 33, 112, 37] have used different definitions; and debate continues about how, or whether, resilience differs from "fault tolerance" or "dependability." Avizienis et al. [9] considered it synonymous with "fault tolerance" and defined it as a wide collection of techniques. The authors defined "dependability" as the "ability to avoid services failures that are more frequent and more severe than is acceptable." In HPC, service failure has two aspects: (1) failure to run a program or incorrect answer and (2) computation taking too long. The second criterion is quantitative and can be measured in various ways, in particular by using the workload efficiency metric defined earlier: A system fails if its workload efficiency is below a certain threshold. Accordingly, resilience can be defined as follows:

The collection of techniques for keeping applications running to a correct solution in a timely and efficient manner despite underlying system faults

"Correct," "timely," and "efficient" are context-dependent. In some contexts "correct" may mean "bit reproducible"; in another context, it could mean "within a rounding error"; in yet another context, we could be content with a system that frequently provides a correct solution to a problem—provided that we can efficiently verify solutions. "Timely" and "efficient" are relative rather than absolute (as in before the hurricane arrives and within our power budget). The definition of "efficient" also depends on what we consider to be the total system—for example, are programming costs included?

#### 3 Sources and Rates of Hardware Faults and Errors

Editor: Mattan Erez

Contributors: Pradip Bose, Paul Coteus, Al Geist, Subhasish Mitra, Rob Schreiber

In this section we describe a generic HPC machine along with the various hardware errors and failures that can occur while it is executing an application. We focus on hardware aspects and do not account for any masking or handling in software. We summarize the rates at which these errors and component failures occur on current systems and then discuss models for the underlying fault mechanisms, project these models to future 11 nm technology, and recommend possible mitigation techniques and their overheads.

#### 3.1 Generic Machine Model and Associated Errors and Failures

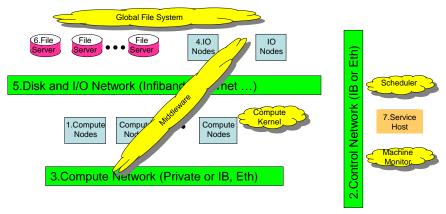

Figure 4 describes a generic exascale machine, patterned after the current generation of HPC machines at Argonne, Los Alamos, Lawrence Livermore, and Oak Ridge National Laboratories and similar leading supercomputing centers. Faults can occur in any part of the machine, with differing consequences. Some failures (fans, power converters) are masked by redundant hardware. Other failures (nodes) will cause an application to crash and restart from the last checkpoint with a new set of nodes but will not cause the system to crash. Some failures cause the entire system to crash and have to be rebooted. The severity of different failures can be measured by the loss of machine time they cause. The masked failure of a fan slightly increases scheduled downtime; a system crash causes the entire machine to be down for half an hour or more.

To expand on the hierarchy, we imagine that the nodes, servers, and switches of the machine are composed of *field replaceable units* (FRUs): processors, memory DIMMs, various circuit cards, power and

Fig 1: Generic Exascale Machine.

Fails can occur in any system 1-7 with differing consequences, 1 being the least troublesome and 7 being the most.

Figure 4: Generic exascale machine

fan modules, and the like, which are usually collected into removable and field serviceable drawers. Sets of drawers may form chassis, and multiple chassis form racks. Typically, but not always, communication is highest between FRUs on a processor node (formed of one or more processor sockets sharing coherent memory and with at least one network connection). This then is a natural fault containment region. Further, groups of nodes may share some common resource—a network adapter card, power supply, or fan module—making this group of nodes in a drawer (or chassis) a higher-level containment region. The entire rack, perhaps sharing a common resource such as a power cord and bulk AC-DC power supply, could form an even higher containment region. However, HPC applications are tightly coupled, so that errors propagate quickly across components. Software help is needed in order to avoid error propagation and transform physical fault containment units into logical error containment units.

#### 3.2 Classification of Errors and Failures

Hardware faults can result in errors and failures that may be grouped into three categories: (1) detected and corrected by hardware (DCE), (2) detected in hardware but flagged as being uncorrectable (DUE), and (3) silent (SE). A silent fault may be masked; a *silent data corruption* (SDC) is an error caused by an unmasked silent fault. We describe these categories below and discuss the possibility that faults may lead to operating with degraded performance, efficiency, and/or fault protection capability.

**Examples of DCE:** (a) a detected error in an error checking and correcting (ECC) protected SRAM/DRAM array that is corrected "in place" before being passed on to a unit that consumes that piece of data and (b) a detected parity error in the processor pipeline that triggers an instruction retry mechanism, resulting in recovery of an uncorrupted, prior-architected register state and re-execution from that point. In the latter case, the recovery mechanism must ensure that leakage of potentially corrupted data to the system's memory or I/O state is prevented during the whole "detection and recovery" process. The system can be architected such that DCEs are usually transparent to the user (application) program and possibly even to supervisory system software (e.g., operating system). In some cases the supervisory system or operating system is invoked in order to help record DCE statistics in system memory for later error analysis. In such cases, the DCE is still transparent to the user application. Usually, hardware has autonomous (software-transparent) mechanisms to record DCE statistics in hardware trace (debug) arrays for later diagnostics. Note that frequent DCEs will slow the system and could, in extreme cases, cause timing errors.

**Examples of DUE:** (a) a double-bit error, detected during the attempted reading of a SECDED ECC-protected SRAM/DRAM array datum, that could not be corrected "in place" and (b) a detected parity error in the processor pipeline that cannot inform the on-chip recovery mechanism within a stipulated deadline, which is an architected parameter designed to ensure that known (potentially) corrupted data is not released to system memory or I/O state. Usually, all DUEs are flagged as an exception to system software by the hardware. Depending on the nature (severity) of the DUE and the capability of the system, the software should be able to handle the hardware-raised exception in a manner that enables one of the following three actions: (i) restart of the processor execution from a local or global checkpoint; (ii) application checkstop that terminates the application, without crashing the node; or (iii) system checkstop that results in a machine check (requiring "reboot") for the particular node or, in the worst case, perhaps even the whole system. In some cases it might be preferable to simply mark corrupted values as invalid, or poisoned, and allow the application itself to handle the error. An example is to use NaN values to prevent incorrect data from silently corrupting results, while still allowing for potential application-level masking or handling.

**Examples of SDC:** (a) an undetected arithmetic computation error, within an integer or floating-point data path pipeline, that makes it into architected register state (and eventually perhaps the system memory state) without triggering any error alert at the hardware level; (b) an undetected control error that results in a premature termination of an iterative loop computation that may result in a datum held in register or memory state to contain a value that is incorrect from a program-intended perspective; and (c) incorrect memory and network transfers that were not detected by the error protection mechanisms (e.g., triple-bit errors with SECDED protection). Such SDCs may eventually be detected within a self-checking application program or as a result of a triggered DUE, but such a detection could happen many thousands, millions, or billions of cycles beyond the point of the original occurrence of the SDC. Thus, a sophisticated "root cause analysis" of a DUE may later point to a an originating (causative) SDC when it comes to proper accounting statistics of various categories of errors in the hardware.

As a consequence of errors originating from hardware sources, and the associated error-handling hierarchy in hardware and/or software, the overall computing system may manifest degraded levels of quality of service as viewed by the end user. For example, if the system encounters a node failure, even if the system or application can recover from the failure, the system will operate at a degraded performance level during the period of system reconfiguration (via updates in the routing tables, etc.). Similarly, an escalated sequence of ECC memory errors may eventually result in a memory "chipkill" that reduces the amount of available system memory (before the defective memory module is replaced), thereby degrading performance. Similarly, certain other repair actions resulting from the flagging of hardware errors may reduce the capability of hardware in terms of being able to detect the full range of errors that the system was originally designed for.

#### 3.3 Quantification of Component Errors and Failures

Table 1 shows the hardware error and failure data for 382 days of the Intrepid system at Argonne National Laboratory. This 40-rack, 557 TF Blue Gene/P system currently shows a mean time to (hardware) interrupt of 7.5 days. Thus, the total of any detected hardware failure, including compute nodes, I/O nodes, compute node interconnect, control hosts, and file servers, was roughly 1 per 7.5 days. This was extremely close to the 7-day MTBF predicted for the machine back in 2006, well before installation, and shows that one can accurately predict hardware failure rates on a large system before its construction. We point out that this agreement was obtained only after wholesale replacement of two minor but problematic elements of the machine—the 10 Gb/s optical transceiver modules on the I/O links and early versions of the bulk power supply modules. This experience is consistent with the LANL study discussed in Section 2.12: In the beginning there is chaos; statistical regularity takes over when the system matures.

Table 1: Error and failure rates for the Intrepid Blue Gene/P system.

| Detected Uncorrectable | Predicted % Fails per Repair Period | Intrepid (ANL 40 racks)<br>Observed failures per Repair Period | Intrepid without I/O Fail-<br>ures per Repair Period |

|------------------------|-------------------------------------|----------------------------------------------------------------|------------------------------------------------------|

| Compute cards          | 90%                                 | 0.648                                                          | 0.648                                                |

| Node boards            | 5%                                  | 0.137                                                          | 0.137                                                |

| I/O cards              | 2%                                  | 0.785                                                          | 0.000                                                |

| Link cards             | 2%                                  | 0.020                                                          | 0.020                                                |

| Service cards          | 1%                                  | 0.098                                                          | 0.098                                                |

| Fans                   | 0%                                  | 0.000                                                          | 0.000                                                |

| Bulk power             | 0%                                  | 0.000                                                          | 0.000                                                |

| Mid-planes             | 0%                                  | 0.000                                                          | 0.000                                                |

| Clock card             | 0%                                  | 0.000                                                          | 0.000                                                |

|                        |                                     | 1.69                                                           | 0.90                                                 |

| Detected | and    | Corrected  | /Markad   |

|----------|--------|------------|-----------|

| Detected | 211111 | i orrecten | / VIAPKEO |

|                           | -   | 3.71  | 3.71  |

|---------------------------|-----|-------|-------|

| Clock card                | 0%  | 0.000 | 0.000 |

| Mid-planes                | 0%  | 0.000 | 0.000 |

| Bulk Power                | 6%  | 0.884 | 0.884 |

| Fans                      | 4%  | 0.079 | 0.079 |

| Service cards             | 1%  | 0.196 | 0.196 |

| Link Cards                | 2%  | 0.059 | 0.059 |

| IO Cards                  | 0%  | 0.000 | 0.000 |

| Node boards               | 28% | 0.491 | 0.491 |

| Compute Cards: (80% DRAM) | 58% | 2.003 | 2.003 |

Not all failures have the same impact. A node board failure affects all 32 compute cards sitting on it (each card contains a 4-core processor and attached memory). The failure of an I/O card can affect all compute cards on the board containing the I/O card. The failure of a link card affects an entire partition or set of nodes that are assigned to a running job.

#### 3.4 Hardware Fault, Error, and Failure Models and Projections

To project the hardware error and failure rates expected in an exascale machine, one must understand the root cause of these events. While reasonably good models exist for some faults in some components, important gaps remain in the projections we will be able to make. We summarize our best-effort models below.

#### 3.4.1 Compute Node Soft Errors

Soft errors in the compute node (processor and memory only; network, power, and cooling are discussed later in this section) are most often a result of events that are entirely external to the system and cannot be

replicated. By far the most significant source of transient faults is energetic particles that interact with the silicon substrate and either flip the state of a storage element or disrupt the operation of a combinational logic circuit. The two common sources of particle strike faults are alpha particles that originate within the package and high-energy neutrons. Alpha particles are charged and may directly create electron-hole pairs. When a high-energy neutron interacts with the silicon die, it creates a stream of secondary charged particles. These charged particles then further interact with the semi-conductor material, freeing electron-hole pairs. If the charged particle creates the electron-hole pairs within the active region of a transistor, a current pulse is formed. This current pulse can directly change the state of a storage device or can manifest as a wrong value at the end of a combinational logic chain.

To analyze the impact a particle strike has on a compute node, we model the effect on each node component separately, namely, SRAM, latches, combinational logic, DRAM, and NVRAM. We then determine a rough estimate for the number of units of each component within the node. We use this estimate to provide a rough order-of-magnitude fault rate for the compute node. We also briefly mention how such faults are handled in processors today, and we discuss how advances in process technology are expected to affect these soft faults. We make projections for the impact of particle-strike soft errors on a future 11 nm node, as well as present an estimate of the overhead/error-rate tradeoffs at the hardware level. The estimates are based on the models below and on some assumptions about the components of a node, as shown in Table 2. First, however, we give a few important caveats about the models and projections.

- The numbers summarized in Table 2 do not include errors due to hard faults or to transient faults

other than particle strikes. We expect those to be a significant contributor to software-visible errors

and failures.

- We do not have access to good models for the susceptibility of near-threshold circuits and do not consider such designs.

- We give only a rough, order-of-magnitude (at best) estimate; many important factors remain unknown with respect to a 11 nm technology node.

We expect that, over the next few years, ongoing research at microelectronic companies, research labs, and academia will provide more accurate estimates.

Table 2: Summary of assumptions on the components of a  $45~\mathrm{nm}$  node and estimates of scaling to  $11~\mathrm{nm}$ .

|                                | 45 nm                                                   | 11 nm                                                   |

|--------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| Cores                          | 8                                                       | 128                                                     |

| Scattered latches per core     | 200,000                                                 | 200,000                                                 |

| Scattered latches out of cores | $\frac{\sqrt{n_{cores}} \times 1.25}{n_{cores}} = 0.44$ | $\frac{\sqrt{n_{cores}} \times 1.25}{n_{cores}} = 0.11$ |

| FIT per latch                  | $10^{-1}$                                               | $10^{-1}$                                               |

| Arrays per core (MB)           | 1                                                       | 1                                                       |

| FIT per SRAM cell              | $10^{-4}$                                               | $10^{-4}$                                               |

| Logic FIT / latch FIT          | 0.1-0.5                                                 | 0.1-0.5                                                 |

| DRAM FIT (per node)            | 50                                                      | 50                                                      |

**SRAM.** Large SRAM arrays dominate the raw particle-strike fault rate of a processor silicon die. When a particle strike releases charge within an active region of a transistor in an SRAM cell, the charge collected may exceed the charge required to change the value stored in the cell, causing a *single event upset* (SEU).

Table 3: Summary of per-processor particle-strike soft error characteristics within a compute node (sea level, equator). Note that other sources of transient faults cannot be ignored.

|                          |             | A              | rray Inter | leaving and SI<br>(Baseline) | ECDED           |                        |  |

|--------------------------|-------------|----------------|------------|------------------------------|-----------------|------------------------|--|

|                          | DCE [F      | IT]            | DUE [FIT]  |                              |                 | SE [FIT]               |  |

|                          | 45 nm       | 11 nm          | 45 nm      | 11 nm                        | 45 nm           | 11 nm                  |  |

| Arrays                   | 5000        | 100000         | 50         | 20000                        | 1               | 1000                   |  |

| Scattered latches        | 200         | 4000           | N/A        | N/A                          | 20              | 400                    |  |

| Combinational logic      | 20          | 400            | N/A        | N/A                          | 0               | 4                      |  |

| DRAM                     | 50          | 50             | 0.5        | 0.5                          | 0.005           | 0.005                  |  |

| Total                    | 1000-5000   | 100000         | 10–100     | 5000-20000                   | 10-50           | 500-5000               |  |

|                          |             |                |            | leaving and ¿S               |                 |                        |  |

|                          |             | (11nm o        | verhead:   | $\sim 1\%$ area and          | < 5% <b>p</b> c | ower)                  |  |

|                          | DCE [FIT]   |                | DU         | DUE [FIT]                    |                 | SE [FIT]               |  |

|                          | 45 nm       | 11 nm          | 45 nm      | 11 nm                        | 45 nm           | 11 nm                  |  |

| Arrays                   | 5000        | 100000         | 50         | 1000                         | 1               | 5                      |  |

| Scattered latches        | 200         | 4000           | N/A        | N/A                          | 20              | 400                    |  |

| Combinational logic      | 20          | 400            | N/A        | N/A                          | 0.2             | 5                      |  |

| DRAM                     | 50          | 50             | 0.5        | 0.5                          | 0.005           | 0.005                  |  |

| Total                    | 1500-6500   | 100000         | 10-50      | 500-5000                     | 10-50           | 100-500                |  |

|                          |             | •              | _          | and ¿SECDEI                  |                 |                        |  |

|                          | (45 nm over | head $\sim 10$ | %; 11nm    | overhead: $\sim 2$           | 0% area         | and $\sim 25\%$ power) |  |

|                          | DCE [FIT]   |                | DUE [FIT]  |                              | SE [FIT]        |                        |  |

|                          | 45 nm       | 11 nm          | 45 nm      | 11 nm                        | 45 nm           | 11 nm                  |  |

| Arrays                   | 5000        | 100000         | 50         | 1000                         | 1               | 5                      |  |

| Scattered latches        | 200         | 4000           | 20         | 400                          | 0.01            | 0.5                    |  |

|                          | 20          | 400            | N/A        | N/A                          | 0.2             | 5                      |  |

| Combinational logic      |             |                |            |                              |                 |                        |  |

| Combinational logic DRAM | 0           | 0              | 0.1        | 0.0                          | 0.100           | 0.001                  |  |

An SEU may impact a single SRAM cell or may change the values of multiple adjacent cells. Such *multicell upsets* (MCUs) are also called *burst errors*. A reasonable ballpark figure for SRAM particle-strike upset rate is 1 upset every  $10^7$  hours for 1 Mb of capacity, which is a rate of  $10^{-4}$  FIT/bit [139]. Our best estimates indicate that the SEU rate for SRAM will remain roughly constant as technology scales. While many complex phenomena impact susceptibility, the current roadmap of changes to devices, operating voltage, and scale do not point to extreme changes in susceptibility. What is expected to change is the distribution of MCUs, with a single upset more likely to affect a larger number of cells at smaller scales.

Because the raw FIT/chip from SRAM is high (estimated at roughly 0.5 upsets per year per chip, or multiple upsets an hour in a large-scale HPC system), large arrays are protected with error detection and error correction capabilities. An approach in use today is a combination of physical word interleaving coupled with an error detection code or with ECC mechanisms. Given the distribution of MCUs today, 4-way interleaving with SECDED capabilities per array line is sufficient. Stronger capabilities will likely be needed in the future, but their energy and area overhead are expected to be low (see Table 3). Note that

our estimates assume that 4-bit or larger bursts increase from 1% of all SEUs to 10% or higher between 45 nm and 11 nm technology and that the rate of bursts of 8 bits or larger increases from 0.01% of all SEUs to 1% of all SEUs [81].

Note that alternative storage technology with much lower particle-strike error rates is possible. Some current processors use embedded DRAM for large arrays, and future processors may use on-chip arrays of nonvolatile storage. Embedded DRAM has a 100 times or more lower error rate than does SRAM. Nonvolatile storage cells are immune to particle strikes but do display some soft-error fault mechanisms (see discussion below).

**Latches.** The error mechanisms and trends for latches are similar to those of SRAM, and the per-latch SEU rate is expected to remain roughly  $10^{-4}$ – $10^{-3}$  FIT/bit [35]. Given the smaller number of latch cells in a processor today compared with SRAM cells, the overall contribution to error rate of latches is much smaller as well. Future processors will contain a much larger number of latch cells, and protection may be necessary. The protection mechanisms and overheads of latches depend on how the latch is used. Some latches are organized in arrays, like SRAM arrays, while other latches are scattered within logic blocks. Array latches can be protected with interleaving and ECC, although such latches are often accessed with finer granularity than large SRAM arrays, which increases the relative overhead of protection. We include this extra cost in Table 3 and project a higher power overhead than area overhead for protecting arrays in order to account for the added protection of latch arrays that may be needed in future processors.

"Scattered latches" are more difficult to protect, on the one had, because the overhead of interleaving and ECC is exorbitant without the regularity of an array. On the other hand, an error in a scattered latch is often masked by the natural operation of the circuit it is part of. Various estimates exist for the derating factor that should be applied for this natural masking, typically ranging from 90 to 95%. The masking rate may depend on the application and also on the architecture, with more streamlined architecture potentially having a lower rate of masked latch errors. If needed, scattered latches can be protected against particle-strike-induced upsets. The two main techniques that can be applied are hardened latches or a combination of parity prediction from logic with parity checking on a collection of latch bits. Both techniques can be effective but potentially have high overhead if a large fraction of latches must be protected. We show the impact of this overhead in Table 3.

Combinational Logic. The trends we expect for particle-strike-induced soft errors in combinational logic are again consistent with those for SRAM and latches. The raw SEU rate associated with combinational logic can reasonably be estimated at 0.1–0.5 FIT for every 1 FIT contributed by scattered latches within logic blocks [57]. Note that this is the raw upset rate and does not account for logical masking effects. Similar to latches, even if an output of a logic gate is changed, this change is highly unlikely to impact the final result of the circuit. Because the output of a combinational logic path is always a latch, the overall masking rate of combinational logic upsets is most likely close to 99%.

Note that the raw upset rate quoted above already accounts for electrical masking, which results from the SEU current pulse being attenuated as it passes through multiple gates, and for timing or latch masking, which results from the output of the combinational logic being observed for only a fraction of the cycle. As with scattered latches, we expect the raw fault rate to stay roughly constant as technology scales, and application and architecture may impact masking rates. The parity-prediction mechanism that can be used to detect errors in latches, will also detect a large fraction of logic errors. Other techniques for detecting combinational logic soft faults at the hardware level include those based on arithmetic coding [122, 94, 8, 95] and replication [7, 140, 133]. Moreover, electrical masking can be increased by using less area and power-efficient gate designs [72, 99].

**DRAM.** As a rule, DRAM exhibits a fixed rate of particle-strike soft errors per DRAM die, regardless of technology. This rate is roughly 10–20 FIT/device, and a significant fraction affects multiple bits and entire rows, columns, or banks of the DRAM device [144]. Many DRAM devices are required for the capacity of each node. Recent studies have shown that the error rate of DRAM is far higher than the particle-strike soft errors, indicating that hard faults in either the peripheral or signaling circuits are the main cause of problems [136, 79, 144].

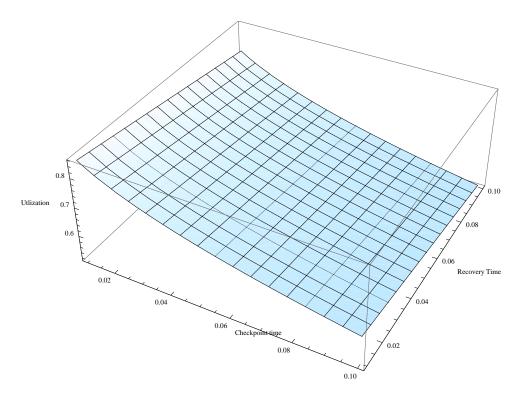

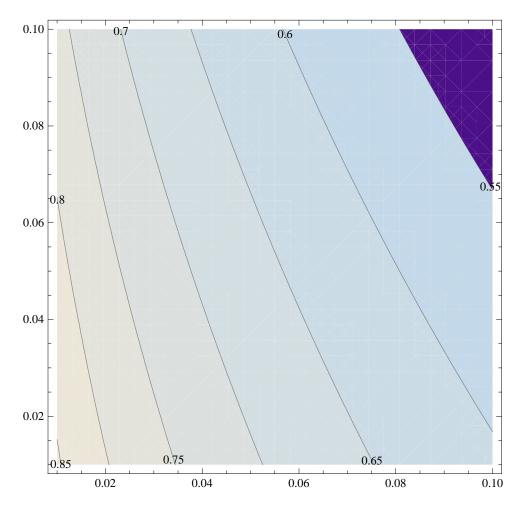

Regardless of the fault mechanism, DRAM is protected with ECC, with large-scale systems typically supporting some form of chipkill-level ECC, which is effective against hard errors as well. We expect that even if new ECC schemes are needed in the future, their overhead will overall be similar to the overhead observed today for most applications.